|

io6Library

WIZnet Dual Stack TCP/IP Ethernet Controller Driver

|

|

io6Library

WIZnet Dual Stack TCP/IP Ethernet Controller Driver

|

Socket register group

.

More...

Macros | |

| #define | _Sn_MR_(N) (_W6100_IO_BASE_ + (0x0000 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| Socket Mode Register Address [R=W][0x00]. More... | |

| #define | _Sn_PSR_(N) (_W6100_IO_BASE_ + (0x0004 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKET n Prefer Source IPv6 Address Register Address [R=W][0x00]. More... | |

| #define | _Sn_CR_(N) (_W6100_IO_BASE_ + (0x0010 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| Socket Command Register Address [RW,AC][0x00]. More... | |

| #define | _Sn_IR_(N) (_W6100_IO_BASE_ + (0x0020 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn Interrupt Register Address [RO][0x00]. More... | |

| #define | _Sn_IMR_(N) (_W6100_IO_BASE_ + (0x0024 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn Interrupt Mask Register Address [R=W][0xFF]. More... | |

| #define | _Sn_IRCLR_(N) (_W6100_IO_BASE_ + (0x0028 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn Interrupt Clear Register Address [WO][0x00]. More... | |

| #define | _Sn_SR_(N) (_W6100_IO_BASE_ + (0x0030 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn Status Register Address [RO][0x00]. More... | |

| #define | _Sn_ESR_(N) (_W6100_IO_BASE_ + (0x0031 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn Extension Status Register Address [RO][0x00]. More... | |

| #define | _Sn_PNR_(N) (_W6100_IO_BASE_ + (0x0100 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn IP Protocol Number(PN) Register Address [R/W][0x0000]. More... | |

| #define | _Sn_NHR_(N) (_Sn_PNR_(N)) |

| Refer to _Sn_PNR_. More... | |

| #define | _Sn_TOSR_(N) (_W6100_IO_BASE_ + (0x0104 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn IPv4 Type of Service(TOS) Register Address [R=W][0x00]. More... | |

| #define | _Sn_TTLR_(N) (_W6100_IO_BASE_ + (0x0108 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn IP Time to live(TTL) Register Address [R=W][0x80]. More... | |

| #define | _Sn_HOPR_(N) (_Sn_TTLR_(N)) |

| Refer to _Sn_TTLR_. More... | |

| #define | _Sn_FRGR_(N) (_W6100_IO_BASE_ + (0x010C << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn Fragment Register Address [R=W][0x4000]. More... | |

| #define | _Sn_MSSR_(N) (_W6100_IO_BASE_ + (0x0110 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn Maximum Segment Size(MSS) Register Address [RW][0x0000]. More... | |

| #define | _Sn_PORTR_(N) (_W6100_IO_BASE_ + (0x0114 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn Source Port Register Address [R=W][0x0000]. More... | |

| #define | _Sn_DHAR_(N) (_W6100_IO_BASE_ + (0x0118 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn Destination Hardware Address Register Address [RW][00:00:00:00:00:00]. More... | |

| #define | _Sn_DIPR_(N) (_W6100_IO_BASE_ + (0x0120 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn Destination IPv4 Address Register Address [RW][0.0.0.0]. More... | |

| #define | _Sn_DIP4R_(N) (_Sn_DIPR_(N)) |

| Refer to _Sn_DIPR_. More... | |

| #define | _Sn_DIP6R_(N) (_W6100_IO_BASE_ + (0x0130 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn Destination IPv6 Address Register Address [RW][::]. More... | |

| #define | _Sn_DPORTR_(N) (_W6100_IO_BASE_ + (0x0140 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn Destination Port Register Address [RW][0x0000]. More... | |

| #define | _Sn_MR2_(N) (_W6100_IO_BASE_ + (0x0144 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn Mode Register 2 Address [R=W][0x00]. More... | |

| #define | _Sn_RTR_(N) (_W6100_IO_BASE_ + (0x0180 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn Retransmission Time Register Address [R=W][0x0000]. More... | |

| #define | _Sn_RCR_(N) (_W6100_IO_BASE_ + (0x0184 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn Retransmission Count Register Address [R=W][0x00]. More... | |

| #define | _Sn_KPALVTR_(N) (_W6100_IO_BASE_ + (0x0188 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn Keep Alive Time Register Address [R=W][0x00]. More... | |

| #define | _Sn_TX_BSR_(N) (_W6100_IO_BASE_ + (0x0200 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn TX Buffer Size Register Address [R=W][0x02]. More... | |

| #define | _Sn_TX_FSR_(N) (_W6100_IO_BASE_ + (0x0204 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn TX Free Buffer Size Register Address [RO][0x0800]. More... | |

| #define | _Sn_TX_RD_(N) (_W6100_IO_BASE_ + (0x0208 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKET TX Memory Read Pointer Register Address[R][0x0000]. More... | |

| #define | _Sn_TX_WR_(N) (_W6100_IO_BASE_ + (0x020C << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn TX Memory Write Pointer Register Address [RW][0x0000]. More... | |

| #define | _Sn_RX_BSR_(N) (_W6100_IO_BASE_ + (0x0220 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn RX Buffer Size Register Address [R=W][0x02]. More... | |

| #define | _Sn_RX_RSR_(N) (_W6100_IO_BASE_ + (0x0224 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn RX Received Size Register Address [RO][0x0000]. More... | |

| #define | _Sn_RX_RD_(N) (_W6100_IO_BASE_ + (0x0228 << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKET RX Memory Read Pointer Register Address[R][0x0000]. More... | |

| #define | _Sn_RX_WR_(N) (_W6100_IO_BASE_ + (0x022C << 8) + WIZCHIP_SREG_BLOCK(N)) |

| SOCKETn TX Memory Write Pointer Register Address [RW][0x0000]. More... | |

Socket register group

.

SOCKETn registers configure and control SOCKETn which is necessary to data communication.

| SOCKETn Control | : _Sn_MR_, _Sn_MR2_, _Sn_CR_, _Sn_IR_, _Sn_IRCLR_, _Sn_IMR_, _Sn_PSR_ |

| SOCKETn Information | : _Sn_SR_, _Sn_ESR_, _Sn_PORTR_, _Sn_DHAR_, _Sn_DIPR_, _Sn_DIP6R_, _Sn_DPORTR_ |

| SOCKETn Retransmission | : _Sn_RTR_, _Sn_RCR_ |

| Internet protocol | : _Sn_MSSR_, _Sn_TOSR_, _Sn_TTLR_, _Sn_FRGR_ |

| Data communication | : _Sn_RX_BSR_, _Sn_TX_BSR_, _Sn_TX_FSR_, _Sn_TX_RD_, _Sn_TX_WR_, _Sn_RX_RSR_, _Sn_RX_RD_, _Sn_RX_WR_ |

| #define _Sn_MR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0000 << 8) + WIZCHIP_SREG_BLOCK(N)) |

Socket Mode Register Address [R=W][0x00].

_Sn_MR_ sets the option or protocol type of SOCKETn before Sn_CR_OPEN is performed.

Each bit of _Sn_MR_ is defined as the following.

| 7 | 6 | 5 | 4 | 3 ~ 0 |

| MULTI/MF | BRDB/FPSH | ND/MC/SMB/MMB | UNIB/MMB6 | P[3:0] |

| P[3:0] | Protocol Mode |

| 0000 | SOCKET Closed |

| 0001 | TCP4 |

| 0010 | UDP4 |

| 0011 | IPRAW4 |

| 0100 | MACRAW |

| 1001 | TCP6 |

| 1010 | UDP6 |

| 1100 | IPRAW6 |

| 1101 | TCP Dual(TCPD) |

| 1110 | UDP Dual (UDPD) |

| #define _Sn_PSR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0004 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKET n Prefer Source IPv6 Address Register Address [R=W][0x00].

_Sn_PSR_ select the Source IPv6 Address to transmit a packet by _Sn_CR_. This function is same as _SLPSR_.

| #define _Sn_CR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0010 << 8) + WIZCHIP_SREG_BLOCK(N)) |

Socket Command Register Address [RW,AC][0x00].

_Sn_CR_ is used to set the command for SOCKET n such as OPEN, CLOSE, CONNECT, LISTEN, SEND, and RECEIVE.

It is automatically cleared to 0x00 after the command is recognized by _WIZCHIP_.

Even though _Sn_CR_ is cleared to 0x00, the command is still being processed.

To check whether the command is completed or not, please check the _Sn_IR_ or _Sn_SR_.

| #define _Sn_IR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0020 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn Interrupt Register Address [RO][0x00].

_Sn_IR_ gets the status of SOCKETn interrupt such as establishment, termination, receiving data, timeout.

If SOCKETn interrupt occurs and the n-th bit of _SIMR_ is set, then SIR_INT(n) is set.

In order to clear the _Sn_IR_ bit, Set the corresponding bit of _Sn_IRCLR_ to 1.

If all _Sn_IR_ bits are cleared, the SIR_INT(n) is automatically cleared.

| 7 ~ 5 | 4 | 3 | 2 | 1 | 0 |

| Reserved | SENDOK | TIMEOUT | RECV | DISCON | CON |

| #define _Sn_IMR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0024 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn Interrupt Mask Register Address [R=W][0xFF].

_Sn_IMR_ is used to mask interrupts of _Sn_IR_.

| #define _Sn_IRCLR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0028 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn Interrupt Clear Register Address [WO][0x00].

_Sn_IRCLR_ clears _Sn_IR_

| #define _Sn_SR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0030 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn Status Register Address [RO][0x00].

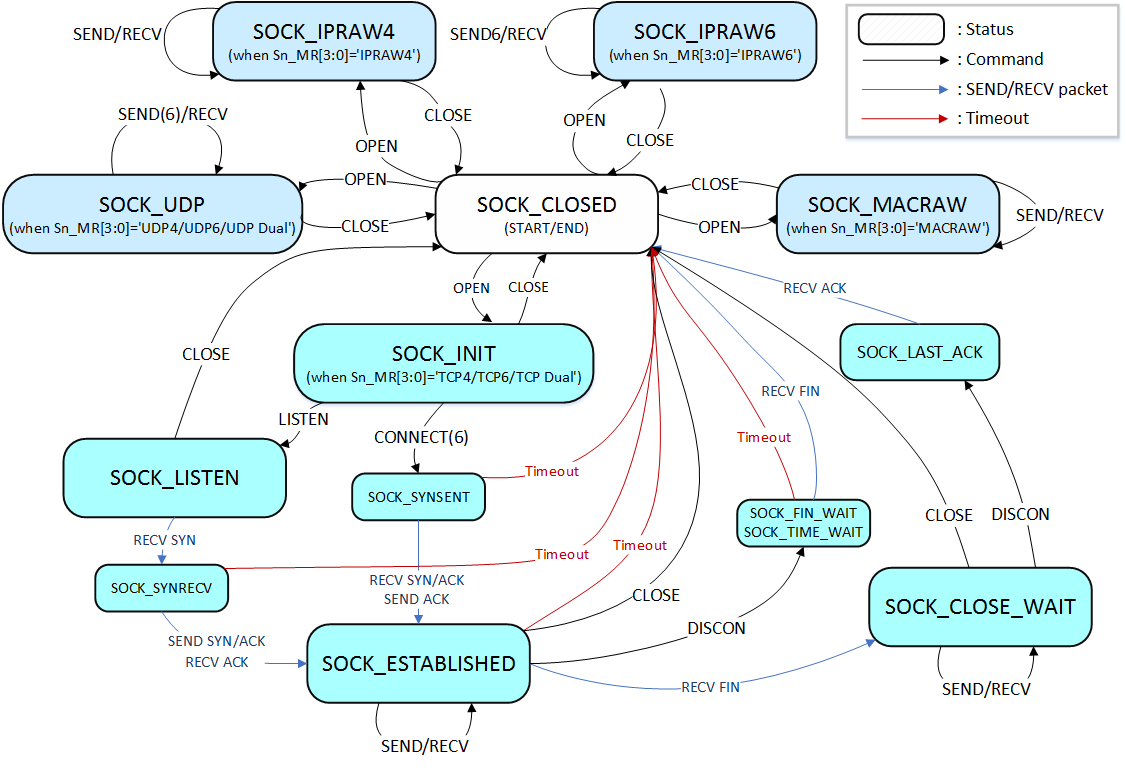

_Sn_SR_ indicates the status of SOCKETn.

The status of SOCKETn can be changed by _Sn_CR_, some TCP packets such as SYN, FIN, RST packet, or Sn_IR_TIMEOUT.

<SOCKETn Status Transition> |

| #define _Sn_ESR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0031 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn Extension Status Register Address [RO][0x00].

_Sn_ESR_ indicates the connected client IP address information such as IP version, IPv6 address type(LLA or GUA),

and TCP operation mode such as TCP SERVER and TCP CLIENT

| 7 ~ 3 | 2 | 1 | 0 |

| Reserved | TCPM | TCPOP | IP6T |

| #define _Sn_PNR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0100 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn IP Protocol Number(PN) Register Address [R/W][0x0000].

_Sn_PNR_ that sets the protocol number/next header field of the IPv4/IPv6 header at the IP layer.

| #define _Sn_TOSR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0104 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn IPv4 Type of Service(TOS) Register Address [R=W][0x00].

_Sn_TOSR_ sets the TOS(Type Of Service) field in IPv4 Header.

| #define _Sn_TTLR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0108 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn IP Time to live(TTL) Register Address [R=W][0x80].

_Sn_TTLR_ sets the TTL(Time To Live)/HOP(Hop Limit) field in IPv4/IPv6 header at the IP layer.

| #define _Sn_FRGR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x010C << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn Fragment Register Address [R=W][0x4000].

_Sn_FRGR_ sets the fragment flag & offset in IPv4 header.

| #define _Sn_MSSR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0110 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn Maximum Segment Size(MSS) Register Address [RW][0x0000].

_Sn_MSSR_ sets or gets the MTU(Maximum Transfer Unit) of SOCKETn.

The MTU of each protocol is as following.

| _Sn_MR_[3:0] | NETMR2_PPPoE = 0 | NETMR2_PPPoE = '1' |

| Sn_MR_TCP4 | 1 ~ 1460 | 1 ~ 1452 |

| Sn_MR_TCP6 | 1 ~ 1440 | 1 ~ 1432 |

| Sn_MR_UDP4 | 1 ~ 1472 | 1 ~ 1464 |

| Sn_MR_UDP6 | 1 ~ 1452 | 1 ~ 1444 |

| Sn_MR_IPRAW4 | 1 ~ 1480 | 1 ~ 1472 |

| Sn_MR_IPRAW6 | 1 ~ 1460 | 1 ~ 1452 |

| Sn_MR_MACRAW | 1 ~ 1514 | |

| #define _Sn_PORTR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0114 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn Source Port Register Address [R=W][0x0000].

_Sn_PORTR_ sets the source port number of SOCKETn .

| #define _Sn_DHAR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0118 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn Destination Hardware Address Register Address [RW][00:00:00:00:00:00].

_Sn_DHAR_ sets or gets the destination hardware address of SOCKETn.

| #define _Sn_DIPR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0120 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn Destination IPv4 Address Register Address [RW][0.0.0.0].

_Sn_DIPR_(= _Sn_DIP4R_) sets or gets the destination IPv4 address of SOCKETn.

| #define _Sn_DIP6R_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0130 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn Destination IPv6 Address Register Address [RW][::].

_Sn_DIP6R_ sets or gets the destination IPv6 address of SOCKETn.

| #define _Sn_DPORTR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0140 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn Destination Port Register Address [RW][0x0000].

_Sn_DPORTR_ sets or gets the destination port number of SOCKETn.

| #define _Sn_MR2_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0144 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn Mode Register 2 Address [R=W][0x00].

_Sn_MR2_ sets the option of SOCKETn with _Sn_MR_, before Sn_CR_OPEN is performed.

Each bit of _Sn_MR2_ is defined as the following.

| 7 ~ 2 | 1 | 0 |

| Reserved | DHAM | FARP |

| #define _Sn_RTR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0180 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn Retransmission Time Register Address [R=W][0x0000].

_Sn_RTR_ sets the timeout value of packet to be retransmitted by _SLCR_.

| #define _Sn_RCR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0184 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn Retransmission Count Register Address [R=W][0x00].

_Sn_RCR_ sets the retry count value of packet to be retransmitted by _SLCR_.

| #define _Sn_KPALVTR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0188 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn Keep Alive Time Register Address [R=W][0x00].

_Sn_KPALVTR_ sets the auto-retransmission time of KA(Keep Alive) packet.

If the destination can not respond to the KA packet during the time set by _Sn_KPALVTR_,

the connection is terminated, Sn_IR_TIMEOUT is set and then _Sn_SR_ is changed SOCK_CLOSED.

Before the time is expierd, if the destination sends a KA/ACK packet or any packet, the connection is still valid,

_Sn_SR_ remained at SOCK_ESTABLISHED.

| #define _Sn_TX_BSR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0200 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn TX Buffer Size Register Address [R=W][0x02].

_Sn_TX_BSR_ sets the TX buffer size of SOCKETn in the 16KB TX memory.

It can be set only with 0,1,2,4,8, and 16K bytes.

| #define _Sn_TX_FSR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0204 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn TX Free Buffer Size Register Address [RO][0x0800].

_Sn_TX_FSR_ gets the transmittable free size of SOCKETn TX buffer.

| #define _Sn_TX_RD_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0208 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKET TX Memory Read Pointer Register Address[R][0x0000].

_Sn_TX_RD_ gets the start pointer of data to be sent by Sn_CR_SEND.

Sn_CR_SEND / Sn_CR_SEND6 starts to transmit the saved data from _Sn_TX_RD_ to _Sn_TX_WR_ in the SOCKETn TX Buffer,

and when Sn_IR_SENDOK is set, It is automatically increased to equal _Sn_TX_WR_.

| #define _Sn_TX_WR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x020C << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn TX Memory Write Pointer Register Address [RW][0x0000].

_Sn_TX_WR_ gets the start pointer of data to be saved in the SOCKETn TX buffer,

or sets the end pointer of data to be sent by Sn_CR_SEND.

If you have completed to save the data to be sent in the SOCKETn TX buffer, increase it as many as the saved size of data before Sn_CR_SEND is performed.

Sn_CR_SEND starts to transmit the saved data from _Sn_TX_RD_ to _Sn_TX_WR_ in the SOCKETn TX Buffer,

and when Sn_IR_SENDOK is set, _Sn_TX_RD_ is automatically increased to equal it.

| #define _Sn_RX_BSR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0220 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn RX Buffer Size Register Address [R=W][0x02].

_Sn_RX_BSR_ sets the RX buffer size of SOCKETn in the 16KB RX memory.

It can be set only with 0,1,2,4,8, and 16K bytes.

| #define _Sn_RX_RSR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0224 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn RX Received Size Register Address [RO][0x0000].

_Sn_RX_RSR_ gets the received data size of SOCKETn RX buffer.

| #define _Sn_RX_RD_ | ( | N | ) | (_W6100_IO_BASE_ + (0x0228 << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKET RX Memory Read Pointer Register Address[R][0x0000].

_Sn_RX_RD_ gets the start pointer of the received data in the SOCKETn RX buffer,

or sets the end data pointer of the read completed data by Sn_CR_RECV.

You can read the received data from it to _Sn_RX_WR_ in the SOCKET RX buffer.

After completing to read data, you should increase it as many as the read size before Sn_CR_RECV is performed.

| #define _Sn_RX_WR_ | ( | N | ) | (_W6100_IO_BASE_ + (0x022C << 8) + WIZCHIP_SREG_BLOCK(N)) |

SOCKETn TX Memory Write Pointer Register Address [RW][0x0000].

_Sn_TX_WR_ gets the end pointer of the data that has been completely received in the SOCKETn RX buffer.

Whenever a data has been completely received from a destination,

It is automatically increased as many as the sum size of the received data and the 'PACKET INFO'.

You can read the recevied data from _Sn_RX_RD_ to it in the SOCKET RX buffer.

1.8.17

1.8.17