Možná jste slyšeli o \(I^2C\) nebo ji již používáte, ale rozumíte jak to funguje? Tento článek je o tom.

Co to je \(I^2C\)

Sběrnice I²C (Inter-Integrated Circuit) je de facto celosvětový standard, který je implementován ve více než 1000 různých integrovaných obvodech více než 50 společností, které vyrábějí elektronické součástky.

Dále je I²C universální sériová komunikační sběrnice, která využívá architekturu multi-master-slave. Používá se v různých řídících architekturách jako System Management Bus (SMBus), Power Management Bus (PMBus), Inteligent Platform Management Interface (IPMI), Display Data Channel (DDC) a Advanced Telecom Computing Architecture (ACTA).

Byla navržena společností Philips na počátku 80. let (nyní NXP Semiconductors). Manuál k současné verzi je zde.

I²C je vhodná pro základní desky, vestavěné systémy nebo komunikaci mezi mobilními telefony a periferními komponenty. I²C je díky své jednoduchosti široce používána pro komunikaci mezi mikrokontroléry a senzorovými poli, displeji, IoT zařízeními, EEPROM atd.

I²C se skládá ze dvou linek, SCL a SDA. Tyto dvě datové linky je třeba připojit k pull-up odporům (na obrázku označen \(R_p\)). Když je sběrnice nečinná, linky SCL a SDA jsou na vysoké úrovni.

Sběrnice I²C funguje podle určitého protokolu. Dále se podívejme na protokol I²C. I²C podporuje více slave (podřízených) zařízení, to znamená, že k jednomu I²C řadiči lze připojit více I²C slave zařízení. Navíc implementuje i více master (nadřízených) zařízení, při komunikaci však může být masterem jenom jedno zařízení.

Tato různá I²C slave zařízení mají různé adresy zařízení, takže hlavní řadič I²C může přistupovat k danému zařízení prostřednictvím jeho I²C adresy.

Linky SDA a SCL musí být připojeny přes pull-up rezistor \(R_p\), obvykle 4.7K (někdy 10K), k napájecímu napětí \(V_{dd}\). Zbytek I²C podřízených jednotek je připojen přímo k linkám SDA a SCL, takže přes linky SDA a SCL lze přistupovat ke všem zařízením nacházejícím se na sběrnici.

Možná jste stále zmatení ohledně I²C, zde jsou některé funkce I²C.

Vlastnosti \(I^2C\)

-

Vyžaduje se jenom jedna datová linka SDA (serial data line) a jedna hodinová linka SCL (serial clock line), SDA (sériová datová linka) a SCL (sériová hodinová linka) jsou obě obousměrné I/O linky.

SCL (Serial Clock): Sériová hodinová linka, která přenáší signály hodin (CLK), obvykle poskytované hlavním zařízením podřízenému zařízení.

SDA (Serial Data): sériová datová linka, přenos komunikačních dat -

Realizuje skutečnou multi-master sběrnici, jakékoli zařízení může být použito jako master i slave, ale současně může být pouze jeden master.

-

Může být detekován externím připojením, které je vhodné pro diagnostiku a ladění systémových chyb.

-

Integrované obvody připojené ke stejné sběrnici jsou omezeny pouze maximální kapacitou sběrnice. Bitová rychlost sériového 8bitového obousměrného přenosu dat může dosáhnout 100 Kbit/s ve standardním režimu, 400 Kbit/s v rychlém režimu a až 3,4 Mbit/s ve vysokorychlostním režimu.

-

Proud spotřebovaný na sběrnici je velmi malý. Počet zařízení rozšířených na sběrnici je proto dán především kapacitní zátěží, která je odolná proti vysokému rušení šumem. Přidání ovladače sběrnice může rozšířit kapacitu sběrnice 10krát a přenosová vzdálenost může dosáhnout 15 m; kompatibilní se zařízeními s různými úrovněmi napětí se širokým rozsahem provozních teplot

-

Obvod rozhraní je výstup s otevřeným drainem. Musí být připojen k napájecímu zdroji VCC přes pull-up rezistor. Když je autobus nečinný, obě linky jsou vysoké. Externí zařízení připojená ke sběrnici jsou zařízení CMOS. Koncový stupeň je rovněž obvod s otevřeným drainem.

Přenos dat

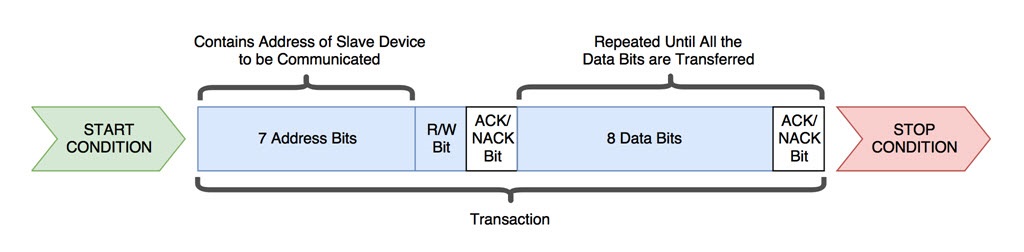

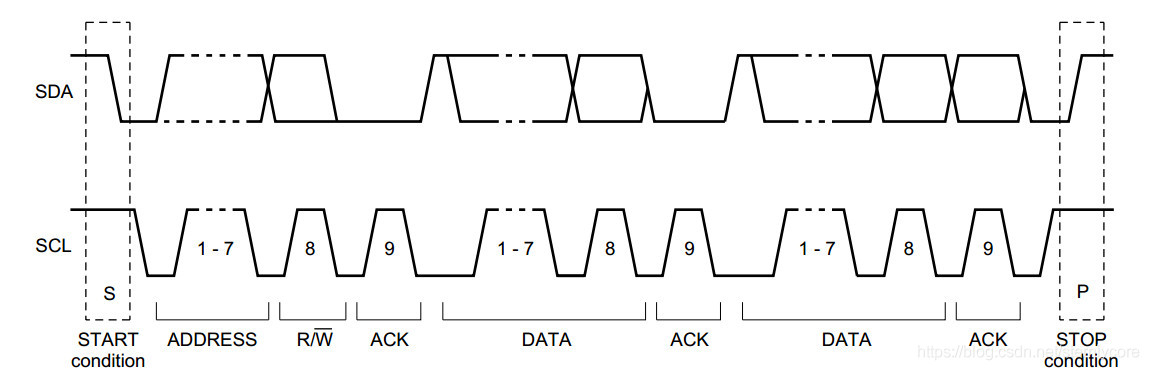

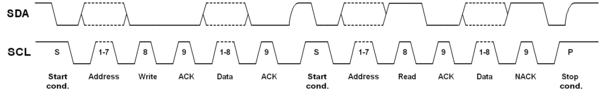

Hlavní zařízení a podřízené zařízení se pro přenos dat řídí následujícím formátem protokolu. Přenos dat sériová data 0 a 1 mezi master a slave zařízeními po datové lince SDA. Strukturu sekvence sériových dat lze rozdělit na:

-

Start Bit

-

Bity adresy (7 bitů nebo 10 bitů)

-

Bit čtení a zápis (1 bit)

-

Bit odezvy (1 bit)

-

Datový bit + bit odezvy (datový bit 8 bitů; bit odezvy 1 bit; data + odezva lze opakovaně přenášet mnohokrát, dokud nenarazí na stop bit)

-

Stop Bit

Start bit

Když se hlavní zařízení rozhodne zahájit komunikaci, musí vyslat spouštěcí signál a je třeba provést následující akce

-

Nejprve přepne SDA z vysoké úrovně na nízkou úrověň

-

Poté změní SCL z vysoké úrovně na nízkou úrověň a začnou tikat hodiny

Poté, co hlavní zařízení signalizuje a spustí tuto podmínku, všechny podřízené jednotky se stanou aktivními i v režimu spánku a budou čekat na přijetí adresového bitu.

Adresový bit

Adresní bity podporují adresy dlouhé 7 bitů anebo 10 bitů. Pokud master potřebuje odeslat/přijmout data na slave, musí nejprve odeslat adresu, pak bude odpovídat slave, pokud se bude shodovat jeho adresa s adresou na sběrnici.

Response Bit má 2 typy:

-

ACK: Slave správně přijímá data nebo bit adresy \+ bity pro čtení a zápis

-

NACK: slave neodpovídá a funguje abnormálně

Pokaždé, když master odešle data a čte a zapisuje bity, bude čekat na signál odpovědi ACK od podřízeného zařízení.

-

Pokud slave zařízení odešle odezvový bitový signál ACK

-

Pokud není k dispozici žádný signál odezvy NACK, SDA vydá VOH, což způsobí, že se hlavní zařízení restartuje nebo zastaví.

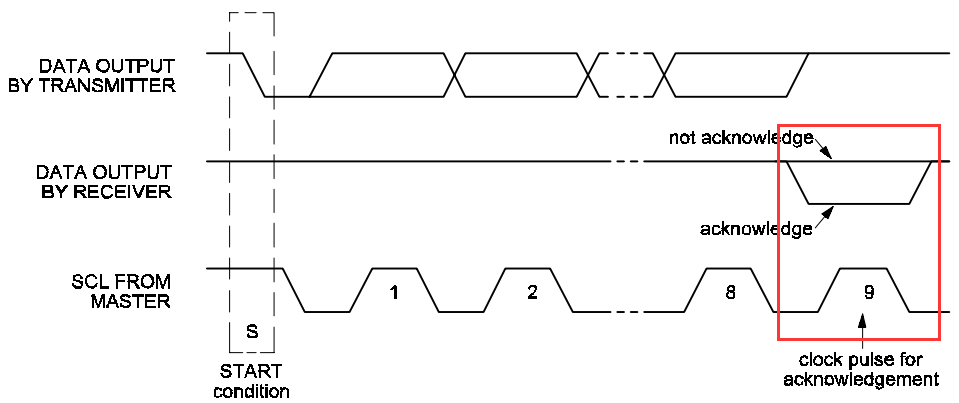

Bit odpovědi

Pokaždé, když jsou data přenášena, má celkem 8 bitů, které nastaví odesílatel a potřebuje přenést datové bity do přijímače.

Po přenosu následuje bit ACK/NACK a pokud přijímač úspěšně přijme data, slave odešle ACK. V opačném případě podřízený odešle NACK.

Data lze odeslat vícekrát, dokud není přijat stop bit.

Datový bit

Když se hlavní zařízení rozhodne ukončit komunikaci, musí odeslat signál ukončení a je třeba provést následující akce.

-

Nejprve se přepne SDA z nízké úrovně 0 na vysokou úroveň 1.

-

Poté se SCL přepne z vysoké úrovně 1 na nízkou úroveň 0.

Stop bit

Když se hlavní zařízení rozhodne ukončit komunikaci, musí odeslat signál ukončení a je třeba provést následující akce.

-

Nejprve se přepn SDA z nízké úrovně 0 na vysokou úroveň 1

-

Poté se SCL přepne z vysoké úrovně 1 na nízkou úroveň 0

Kdo bude řídící

Ve vícehlavním komunikačním systému je na sběrnici je více uzlů, všechny mají své vlastní adresovací adresy, mohou k nim přistupovat ostatní uzly jako podřízené uzly a všechny mohou být použity jako hlavní uzly k odesílání řídicích bajtů a přenosu dat do jiných uzlů. Pokud však dva nebo více uzlů oba pošlou spouštěcí signály na sběrnici a začnou přenášet data, dojde ke konfliktu. K vyřešení tohoto konfliktu je potřeba výběrové rozhodnutí, což je arbitráž na I²C sběrnici.

Rozhodování na sběrnici I²C je rozděleno do dvou částí: synchronizace linky SCL a arbitráž linky SDA.

Synchronizace SCL linky (hodiny)

Synchronizace SCL je způsobena logickou funkcí sběrnice „AND“ (výstup s otevřeným drainem), to znamená, že pokud jeden uzel vysílá nízkou úroveň, na sběrnici se to jeví jako nízká úroveň. Sběrnice se může být ve stavu vysoké úrovně pouze tehdy, když všechny uzly vysílají vysoko. Je to právě díky principu logické funkce řádkové „AND“ přesné, že když více uzlů vysílá hodinové signály současně, je na sběrnici zobrazen jednotný hodinový signál. Toto je princip synchronizace SCL.

Výběr SDA

Arbitráž linky SDA je také založena na principu, že sběrnice má logickou funkci linky „AND“. Poté, co uzel odešle 1bitová data, porovná, zda jsou data prezentovaná na sběrnici konzistentní s tím, co odeslal (podobně jako mechanismus zpětného čtení na sběrnici CAN). Pokud ano, pokračuje v odesílání; jinak sběrnici opustí. Arbitráž linky SDA může zajistit, že systém sběrnice I²C normálně komunikuje a nedojde ke ztrátě dat, když se více hlavních uzlů pokouší ovládat sběrnici současně. Sběrnicový systém umožňuje pouze jednomu hlavnímu uzlu pokračovat v obsazení sběrnice prostřednictvím arbitráže.

Rozhodovací proces mezi dvěma mastery

DATA1 a DATA2 jsou datové signály zasílané hlavním uzlem na sběrnici, SDA je datový signál prezentovaný na sběrnici a SCL je hodinový signál prezentovaný na sběrnici. Když hlavní uzly 1 a 2 vysílají spouštěcí signály současně, oba hlavní uzly vysílají signály vysoké úrovně. V tomto okamžiku je signál na sběrnici vysoký a oba hlavní uzly detekují, že signál na sběrnici je stejný jako signál vysílaný jimi samými, a pokračují v odesílání dat. Ve druhém taktu oba hlavní uzly vysílají signály nízké úrovně a signály prezentované na sběrnici jsou nízkoúrovňové a pokračují v odesílání dat. Ve 3. hodinovém cyklu vysílá hlavní uzel 1 signál vysoké úrovně, zatímco hlavní uzel 2 vysílá signál nízké úrovně. Podle logické funkce řádku „AND“ sběrnice je signál na sběrnici nízkoúrovňový. V tomto okamžiku hlavní uzel 1 detekuje, že data na sběrnici se liší od dat odeslaných jím samotným, a odpojí výstupní stupeň dat a přepne se na podřízený, aby přijal stav. Tímto způsobem hlavní uzel 2 získá sběrnici a data se neztratí, to znamená, že data na sběrnici jsou stejná jako data odeslaná hlavním uzlem 2 a hlavní uzel 1 nadále přijímá data poté, co se změní na slave uzel a také neztratí linku SDA. data. Během arbitrážního řízení proto nedochází ke ztrátě dat.

Shrnutí: SDA arbitráž a zpracování synchronizace hodin SCL nejsou sekvenční, ale provádějí se současně.

Uváznutí (deadlock)

Při skutečném používání je I²C náchylná k uváznutí. Existují dvě běžné situace, kdy dochází k uváznutí:

-

Jedním z nich je, že hlavní zařízení se abnormálně resetuje, když podřízené zařízení odpoví ACK

-

Druhým je, že hlavní zařízení se nenormálně resetuje, když podřízené zařízení odpoví datovým bitem 0

Stejným bodem v obou případech je, že SDA je ve stavu, kdy je podřízené zařízení staženo nízko, když je hlavní zařízení abnormálně resetováno, zatímco SCL je po resetování hlavního zařízení ve stavu VOH (klidový stav). V tomto okamžiku bude podřízené zařízení čekat, až nadřízené zařízení sníží SCL, aby převzalo ACK nebo datový bit, a nadřízené zařízení počká, až podřízené zařízení uvolní linku SDA. Hlavní zařízení a podřízené zařízení na sebe čekají, dívají se na sebe ve vzduchu a přecházejí do stavu uváznutí.

Zde jsou některé běžné způsoby řešení problému uváznutí:

-

Poté, co hlavní zařízení detekuje, že SDA je staženo dolů na více než určitou dobu, aktivně resetuje podřízené zařízení, aby uvolnilo SDA. Předpokladem této metody je, že podřízené zařízení má resetovací kolík a MCU může ovládat resetovací kolík podřízeného zařízení, aby jej resetoval.

-

Poté, co hlavní zařízení detekuje, že SDA je staženo na více než určitou dobu, posunulo 9 hodin na hodinovou sběrnici a vezme bit ACK podřízeného zařízení, takže podřízené zařízení uvolní SDA do VOH.

-

Připojte vyrovnávací paměť I²C do série mezi hlavní a podřízená zařízení, která dokáže automaticky detekovat stavy uváznutí. Když je detekováno uváznutí, aktivně se odpojí od hlavního zařízení a odešle 9 hodin do podřízeného zařízení. Poté, co podřízené zařízení uvolní linku SDA, obnoví spojení s hlavním zařízením.

Problému se zablokováním I²C se nelze zásadně vyhnout. Kromě uváznutí I²C způsobeného abnormálním resetem MCU může podřízené zařízení také abnormálně stáhnout SDA a způsobit uváznutí během normálního komunikačního procesu. Software by proto měl být navržen tak, aby se dokázal zotavit z uváznutí, když dojde k uváznutí, aby mohla komunikace I²C pokračovat.

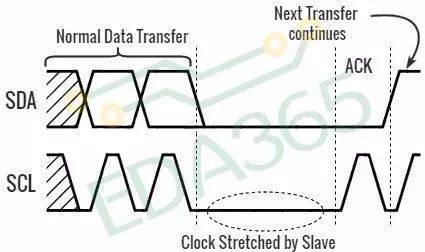

Protahování hodin

Co je to I²C protahování hodin (Clock Stretching)? V komunikačním procesu master-Slave I²C jsou hodiny SCL na sběrnici vždy generovány a řízeny masterem, ale pokud slave nemůže držet krok s rychlostí master, protokol I²C stanoví, že slave může protáhnout SCL hodinovou linka. Přenos je pozastaven, dokud slave zařízení neuvolní linku SCL, a přenos pokračuje.

Clock Stretching je volitelná konfigurace pro slave. Pokud není povoleno, slave nemůže ovládat SCL; pokud je povoleno, může podřízený snížit přenosovou rychlost násilným stažením SCL na nízkou úroveň. Během období, kdy je SCL VOL, může hostitel pouze čekat, až Slave uvolní SCL.

Opakovaný start

Někdy master potřebuje provést vícenásobnou výměnu zpráv v rámci jedné komunikace, jako je přenos zpráv s různými podřízenými zařízeními nebo přepínání operací čtení a zápisu, a nechce být během této doby rušen jiným masterem, pak můžete použít „repeat start“ condition' — Při komunikaci může master vygenerovat více podmínek spuštění pro dokončení výměny více zpráv a nakonec vygenerovat podmínku zastavení pro ukončení celého komunikačního procesu. Vzhledem k tomu, že během této doby nedojde k žádnému zastavení, master stále okupuje sběrnici a ostatní účastníci se nemohou zapnout.

Rozdíly mezi sběrnicemi

| Protokol | Složitost | Rychlost | Počet zařízení | Počet vodičů | Duplex | Počet masterů a slavů |

|---|---|---|---|---|---|---|

UART |

jednoduchá |

nejpomalejší |

2 zařízení |

1 |

full duplex |

jeden na jednoho |

I²C |

je jednoduché přidávat více zařízení |

rychlejší než UART |

do 127, s více zařízeními narůstá složitost |

2 |

half duplex |

mnoho slavů a jeden master |

SPI |

složitá s více zařízeními |

nejrychlejší |

mnoho, s více zařízeními narůstá složitos |

4 |

full duplex |

1 master, mnoho slavů |

Možná se ptáte, která z těchto tří komunikací je nejlepší? Je to UART, I²C nebo SPI? Bohužel neexistuje žádná „nejlepší“ komunikační sběrnice. Každá komunikační sběrnice má své výhody a nevýhody.

Uživatelé by si proto měli vybrat komunikační sběrnici, které nejlépe vyhovují jejich projektu. Pokud chcete například nejrychlejší komunikaci po sběrnici s periferiemi, SPI by bylo ideální. Na druhou stranu, pokud chce uživatel připojit více zařízení, aniž by to bylo příliš komplikované, I²C by bylo ideální, protože může připojit až 127 zařízení a snadno se spravuje.